順序回路

入力のみではなく,現在の状態にも影響される回路

記憶のモデル

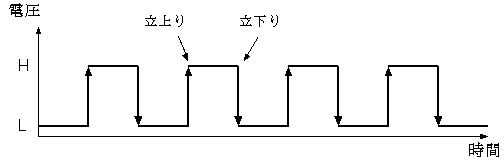

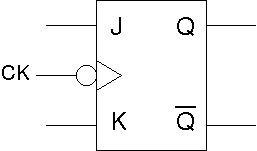

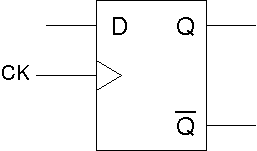

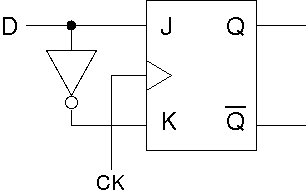

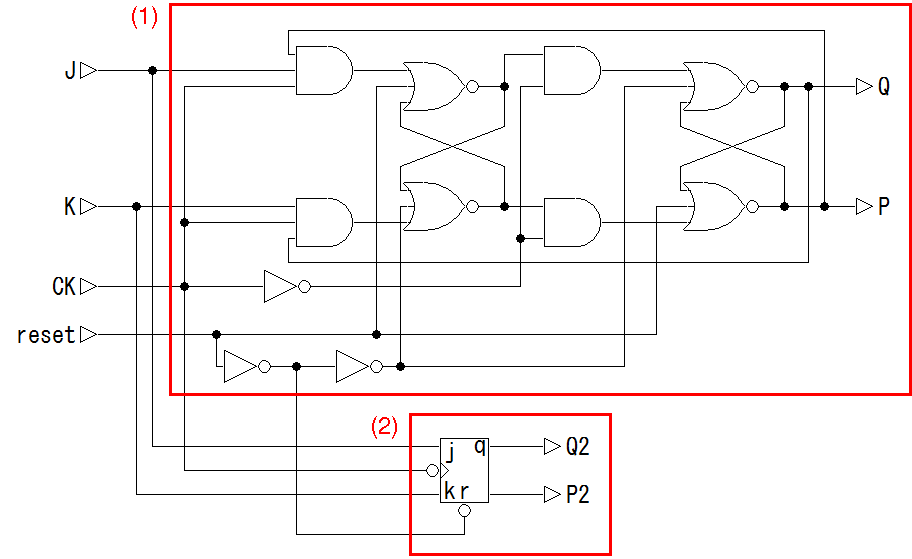

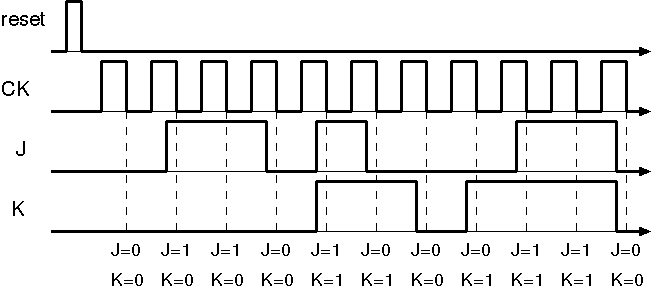

フリップフロップ(flip flop)

|

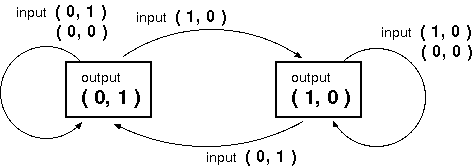

状態遷移図 |

|||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

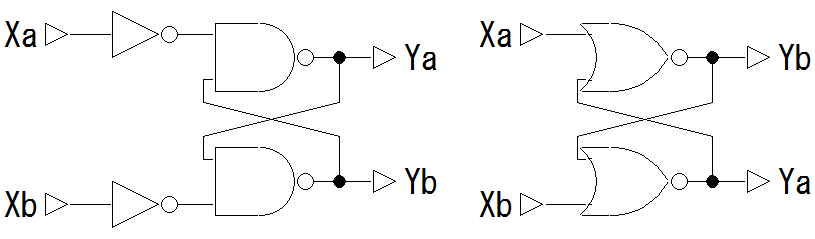

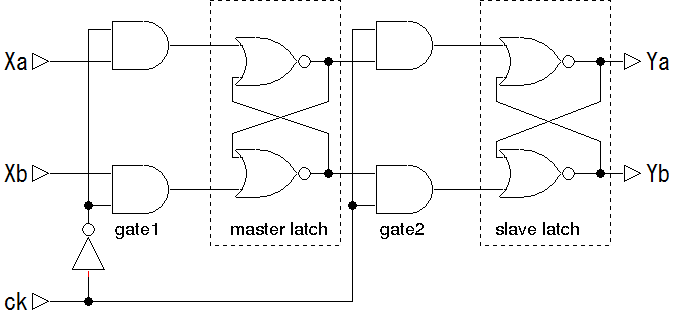

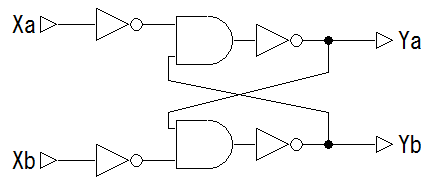

(Xa, Xb)を入力とし,

(Ya, Yb)を出力とする回路.

次の動作をする.

- 入力が(1, 0) のとき,出力も(1, 0)

- 入力が(0, 1) のとき,出力は(0, 1)

- Xa=1, Xb=1 と 同時に 2つの入力に1を入れることはない.

- 入力が(0, 0) のときは, 直前の状態を維持して出力は変わらない.

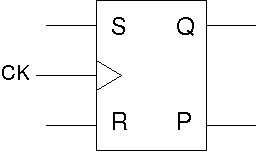

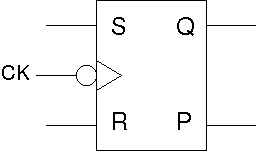

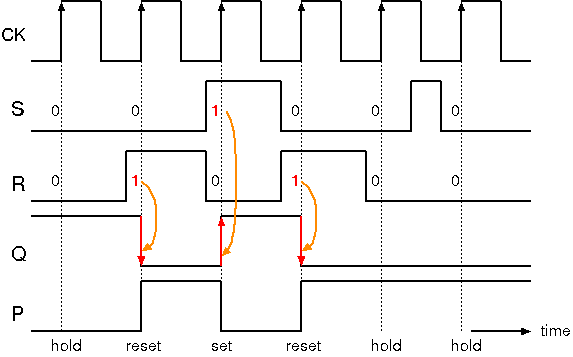

SRフリップフロップ

SR: Set & Reset

ラッチ回路

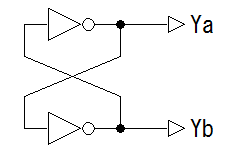

-

広い意味でのSRフリップフロップ回路

- 2つの状態を取り得る

- (Ya, Yb) = (1, 0)の状態

- (Ya, Yb) = (0, 0)の状態

-

ラッチ回路: 上の回路に入力端子(Xa, Xb)を付ける.

- Xa=Xb=0のときは, 上の回路と同様に2つの状態を取り得る

- (Xa, Xb) = (1, 0) のときは, (Ya, Yb) = (1, 0)

- (Xa, Xb) = (0, 1) のときは, (Ya, Yb) = (0, 1)

-

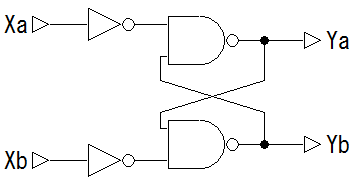

NORゲートで置き換えた回路

- (Xa, Xb) = (1, 0), (Ya, Yb) = (1, 0) の状態から入力が (Xa, Xb = (0, 0) に変化しても, 出力は不変(保持動作)

- (Xa, Xb) = (0, 1), (Ya, Yb) = (0, 1) の状態から入力が (Xa, Xb = (0, 0) に変化しても, 出力は不変(保持動作)